วงจรสาธิตเทคโนโลยีเชิงเส้น 1255 16-BIT 25OKSPS ADC

คำอธิบาย

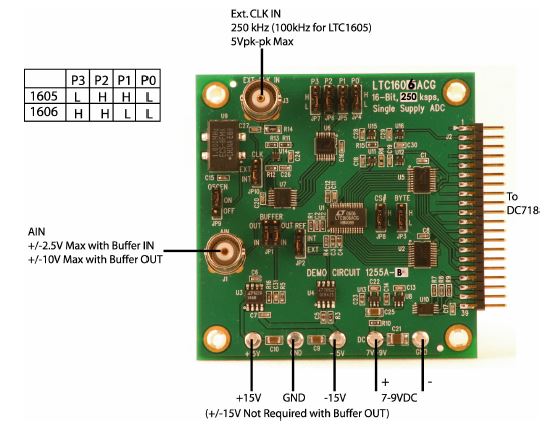

LTC1606 เป็น ADC 250Ksps ที่ดึงพลังงานเพียง 75mW จากแหล่งจ่ายไฟ +5V เดียว ในขณะที่ LTC1605 เป็น ADC 100Ksps ที่ดึงพลังงานเพียง 55mW จากแหล่งจ่ายไฟ +5V sin-gle DC1255 ใช้งานได้ทั้ง 1606 ภาค ข้อความต่อไปนี้อ้างอิงถึง LTC1605 แต่ยังใช้กับ LTCXNUMX ด้วย s ที่เหมาะสมampการพิจารณาความถี่หลิง วงจรสาธิต 1255 ช่วยให้ผู้ใช้ประเมินประสิทธิภาพของ LTC1605/LTC1606 ได้ และมีจุดมุ่งหมายเพื่อสาธิตการต่อสายดิน การวางชิ้นส่วน การกำหนดเส้นทาง และการบายพาสที่แนะนำ ออกแบบ files สำหรับแผงวงจรนี้มีอยู่ โทรไปโรงงานแอลทีซี

ขั้นตอนการเริ่มต้นอย่างรวดเร็ว

เชื่อมต่อ DC1255A เข้ากับบอร์ดรวบรวมข้อมูล USB ความเร็วสูง DC718B โดยใช้ขั้วต่อ J2 เชื่อมต่อ DC718B เข้ากับโฮสต์พีซีด้วยสายเคเบิล USB A/B มาตรฐาน ใช้ไฟ 7V-9V DC กับขั้วต่อ 7V-9V และ GND ใส่ +15V และ -15V ไปที่ขั้วต่อที่ระบุ หากต้องใช้บัฟเฟอร์ภายใน (ค่าเริ่มต้น) ใช้แหล่งสัญญาณกระวนกระวายใจต่ำกับ J1 ในฐานะที่เป็นแหล่งกำเนิดสัญญาณนาฬิกา สามารถใช้นาฬิกาออนบอร์ดหรือคลื่นไซน์ 250kHz 10dBm ที่กระวนกระวายใจต่ำหรือคลื่นสี่เหลี่ยมไปยังตัวเชื่อมต่อ J3 ได้ โปรดทราบว่า J3 มีตัวต้านทานปลายสาย 50• ถึงกราวด์ เรียกใช้ซอฟต์แวร์ QuickEval-II (Pscope.exe เวอร์ชัน K51 หรือใหม่กว่า) ที่มาพร้อมกับ DC718B หรือดาวน์โหลดจาก www.linear.com.

การตั้งค่า

กระแสไฟตรง

DC1255 ต้องใช้กระแสไฟ 7-9VDC ที่ประมาณ 24mA และ +/- 15V ampลิฟายเออร์ U3 หากคุณไม่ได้ใช้ U3 (ดูจัมเปอร์ JP1) คุณไม่จำเป็นต้องจ่าย +/-15V แหล่งจ่ายไฟ 7-9VDC จ่ายไฟให้กับ ADC ผ่านทางตัวควบคุม LT1761-5 ให้การป้องกันอคติย้อนกลับโดยไม่ตั้งใจ ดูรูปที่ 1 สำหรับรายละเอียดการเชื่อมต่อ

แหล่งนาฬิกา

JP10 (CLK) กำหนดว่า DC1255 เป็นแบบอินเตอร์เนล (ค่าเริ่มต้น) หรือโอเวอร์คล็อกภายนอก นาฬิกาภายในประกอบด้วยออสซิลเลเตอร์นาฬิกา ECS 1MHz ซึ่งแบ่งด้วยตัวนับ 74VHC161 ออสซิลเลเตอร์นี้สามารถปิดได้โดยการตั้งค่า JP9 (OSCEN) ไปที่ตำแหน่ง OFF จัมเปอร์ (JP4-JP7) ตั้งค่าอัตราส่วนตัวแบ่งสัญญาณนาฬิกาภายในสำหรับ ADC ที่เหมาะสม (LTC1605 หรือ LTC1606) ดูตารางในรูปที่ 1 สำหรับการตั้งค่าจัมเปอร์ สำหรับนาฬิกาภายนอก คุณต้องจัดให้มีคลื่นไซน์หรือสี่เหลี่ยมที่กระวนกระวายใจต่ำ 10dBm ให้กับ J3 โปรดทราบว่า J3 มีตัวต้านทานการสิ้นสุด 50 ตัวต่อกราวด์ การขับเคลื่อนอินพุตนี้ด้วยตรรกะจะเป็นเรื่องยาก ขอบที่เพิ่มขึ้นอย่างช้าๆ อาจส่งผลต่อ SNR ของคอนเวอร์เตอร์เมื่อมีค่าสูงampสัญญาณอินพุตความถี่สูงกว่าสว่างขึ้น บอร์ดสาธิตรวมวงจรเครื่องตรวจจับขอบไว้ในเอกสารประกอบซอฟต์แวร์ฉบับสมบูรณ์ซึ่งมีอยู่ในเมนูวิธีใช้ สามารถดาวน์โหลดการอัพเดตได้จากเมนูเครื่องมือ ตรวจสอบการอัปเดตเป็นระยะเนื่องจากอาจมีการเพิ่มคุณสมบัติใหม่ ซอฟต์แวร์ Pscope ควรรู้จัก DC1255A และกำหนดค่าตัวเองโดยอัตโนมัติ คลิกปุ่มรวบรวม (ดูรูปที่ 2) เพื่อเริ่มรับข้อมูล อาจจำเป็นต้องกด Collect อีกครั้ง ขึ้นอยู่กับว่า Pscope ใช้บอร์ดใด จากนั้นปุ่มรวบรวมจะเปลี่ยนเป็นหยุดชั่วคราว ซึ่งสามารถคลิกเพื่อหยุดการรับข้อมูลได้ รูปแบบของอินเวอร์เตอร์ (U14) ตามด้วยการหน่วงเวลา 200n วินาที การป้อนพร้อมกับแหล่งสัญญาณนาฬิกาดั้งเดิม คือเกต NAND อินพุต 7 ตัว (U200B) สิ่งนี้จะสร้างพัลส์ต่ำแบบแอคทีฟ ap-ใกล้เคียง 200nsec ที่ ADC หากเวลาสูงสุดของนาฬิกามากกว่า 50nsec โดยทั่วไปจะใช้นาฬิการอบการทำงาน 250% ที่ 3kHz เพื่อทดสอบบอร์ดสาธิตเหล่านี้ พัลส์รอบการทำงานที่สั้นกว่า (แอคทีฟสูงที่ J40) สามารถใช้ได้อย่างน้อย XNUMXnsec

เอาท์พุตข้อมูล

เอาต์พุตข้อมูลแบบขนานจากบอร์ดนี้ (0V-3.3V) หากไม่ได้เชื่อมต่อกับ DC718 สามารถรับได้โดยลอจิกอานาไลเซอร์ แล้วนำเข้าสู่สเปรดชีตหรือแพ็คเกจทางคณิตศาสตร์ในภายหลัง ขึ้นอยู่กับรูปแบบของการประมวลผลสัญญาณดิจิทัลที่ต้องการ

จัมเปอร์ BYTE และ CS#

โดยทั่วไปบอร์ดสาธิตจะจัดส่งโดยมี BYTE (JP3) และ CS# (JP8) เชื่อมโยงกับกราวด์ หากคุณตั้งใจจะใช้งานอุปกรณ์นี้ในลักษณะที่เกี่ยวข้องกับสายเหล่านี้ คุณสามารถใช้จัมเปอร์เพื่อแนะนำสัญญาณเหล่านี้จากแหล่งภายนอกได้

อ้างอิง

JP2 อนุญาตให้คุณเลือกการอ้างอิงบนชิปหรือ LT1019A-2.5 ภายนอก (ค่าเริ่มต้น) เป็นข้อมูลอ้างอิง ข้อมูลจำเพาะดริฟท์ทั่วไปของการอ้างอิงภายนอกนั้นคล้ายคลึงกับการอ้างอิงบนชิป แต่ LT1019-2.5 รับประกันค่าสูงสุด

อนาล็อก

บอร์ดสาธิตจัดส่งมาพร้อมกับ JP1 ในตำแหน่ง ''IN'' ซึ่งในกรณีนี้คืออินพุต ampลิไฟเออร์อยู่ในเส้นทางสัญญาณ เมื่อ JP1 อยู่ในตำแหน่ง ''IN'' U3 (LT1468) จะให้เกนที่เพิ่มขึ้น 9dB ซึ่งจะช่วยให้เครื่องกำเนิดสัญญาณที่มีระดับเอาต์พุต 2.5V RMS สามารถขับเคลื่อนตัวแปลงให้เต็มสเกลได้ นี้ ampลิฟายเออร์ไม่กระทบต่อ SNR หรือประสิทธิภาพการบิดเบือนของคอนเวอร์เตอร์ ความหนาแน่นของสัญญาณรบกวนอินพุตของ LT1468 เองคือ 5nV/•Hz ในวงจรตามที่กำหนดค่าไว้ อิมพีแดนซ์เครือข่ายป้อนกลับและ ampสัญญาณรบกวนอินพุตของ lifier ในปัจจุบันช่วยลดเสียงรบกวน เพื่อสร้างความหนาแน่นของสัญญาณรบกวนอ้างอิงอินพุตที่ 7.44nV/•Hz ด้วยอัตราขยาย 2.82 ทำให้เกิดสัญญาณรบกวน 17uV RMS ในย่านความถี่ 675kHz ที่กำหนดโดยตัวแปลง นี่คืออัตราส่วนสัญญาณต่อเสียงรบกวนที่ 112dB ที่เต็มสเกล แน่นอนว่าสิ่งนี้ไม่สามารถตรวจสอบได้ที่เอาต์พุตของ ADC เมื่อ JP1 อยู่ในตำแหน่ง ''OUT'' อิมพีแดนซ์อินพุตที่ J1 คือ 10K• เมื่อ JP1 อยู่ในตำแหน่ง ''IN'' ความต้านทานอินพุตจะสูงมาก ถ้า J1 ขับเคลื่อนโดยเครื่องกำเนิดไฟฟ้าที่มีจุดประสงค์เพื่อขับเคลื่อนอิมพีแดนซ์ 50• คุณอาจต้องการใช้เทอร์มิเนเตอร์ขนาด 50• หากจะต้องประเมินแหล่งความต้านทานที่สูงกว่า คุณจะเห็นผลลัพธ์ที่ดีกว่าด้วย ampli-fier ในเส้นทางสัญญาณ หากคุณต้องการประเมินผล ampตัวขยายสัญญาณในเอกภาพ, ย้าย R5 ใหม่หรือประสานตัวต้านทานค่าต่ำขนานกับ R16 หากคุณต้องการประเมินผล amplifier ที่มีอัตราขยายสูงกว่า คุณอาจลดค่า R5 ได้ หากคุณใช้ตัวต้านทานคุณภาพสูงมาก คุณควรจะเพิ่มเกนได้ถึง 50 ก่อนที่ระดับเสียงรบกวนของคอนเวอร์เตอร์จะเพิ่มขึ้นอย่างเห็นได้ชัด ฉบับที่tage เพิ่มขึ้น 10 ควรส่งผลให้ SNR โดยทั่วไปที่ 90dB ลดลงเหลือ 89.9dB ฉบับที่tage เพิ่มขึ้น 50 ควรให้ประมาณ 88.7dB และเพิ่มขึ้น 100 จะให้ประมาณ 86dB SNR THD จะเพิ่มขึ้น แต่เมื่อเพิ่มขึ้น 50 THD ของ LT1468 โดยทั่วไปจะยังอยู่ในช่วง -90dB

หากมีการ amplifier ได้รับการกำหนดค่าเพื่อให้ได้อัตราขยายที่สูง ความต่างศักย์กราวด์ระหว่างเครื่องมือต่างๆ บนม้านั่งของคุณอาจพบว่ามีการพัฒนาส่วนประกอบที่แตกต่างกันที่อินพุตไปยังบอร์ดสาธิต อาจจำเป็นต้องแยกหม้อแปลงเพื่อให้ได้ผลลัพธ์ที่ดีโดยมีค่าเพิ่มขึ้น 50

การรวบรวมข้อมูล

ระบบที่ใช้สำหรับการรวบรวมข้อมูลอาจมีผลเสียต่อประสิทธิภาพของบอร์ดสาธิต หากสร้างกระแสไฟฟ้ากราวด์จำนวนมากผ่านบอร์ดสาธิต บอร์ดสาธิตนี้ได้รับการทดสอบภายในบริษัทโดยการจำลอง FFT plot ที่แสดงไว้ที่ด้านซ้ายล่างของหน้าที่ 6 ของเอกสารข้อมูล LTC1606 สิ่งนี้เกี่ยวข้องกับการใช้แหล่งสัญญาณนาฬิกาที่กระวนกระวายใจต่ำ 250kHz สำหรับนาฬิกาเข้ารหัส ร่วมกับเครื่องกำเนิดสัญญาณไซน์ซอยด์ที่มีสัญญาณรบกวนต่ำและความผิดเพี้ยนต่ำที่ความถี่ใกล้เคียง 1KHz ที่ amplifier คือ ''IN'' สำหรับการทดสอบภายใน และระดับสัญญาณอินพุตจะอยู่ที่ประมาณ -1dBfs FFT ที่แสดงในแผ่นข้อมูลคือ FFT 4096 จุด โดยมีความถี่อินพุตที่ 1037.5976Hz อย่างแม่นยำ ความถี่นี้เป็น ''ที่สอดคล้องกัน'' (สร้างจำนวนรอบของความถี่พื้นฐานภายในหน้าต่าง) สำหรับความถี่สัญญาณนาฬิกา 250kHz และจำนวนเฉพาะของรอบ (17 รอบ) จำนวนเฉพาะของรอบอินทิกรัลใช้จำนวนรหัสอินพุตที่เป็นไปได้มากที่สุด อัตราสัญญาณนาฬิกาอื่นๆ ต้องการความถี่อินพุตที่แตกต่างกันสำหรับสัญญาณที่สอดคล้องกันampหลิง เพื่อคำนวณความถี่อินพุต f สำหรับ s ที่กำหนดampความถี่ลิง fs จำนวน samples n และจำนวนเต็มเฉพาะ m ใช้สูตรต่อไปนี้

มีหลายสถานการณ์ที่สามารถสร้างผลลัพธ์ที่ทำให้เข้าใจผิดเมื่อประเมิน ADC สิ่งที่พบบ่อยคือการป้อนคอนเวอร์เตอร์ด้วยความถี่ ซึ่งเป็นผลคูณย่อยของ sampอัตรา และซึ่งจะใช้ชุดย่อยเพียงเล็กน้อยของโค้ดเอาท์พุตที่เป็นไปได้เท่านั้น นอกจากนี้ โปรดทราบว่า DC1255 ไม่มีตัวกรองการลบรอยหยัก

จัมเปอร์ต่อไปนี้ JP1 คือตัวกรองความถี่ต่ำผ่านลำดับแรก 800kHz (R1 และ C2) ซึ่งไม่ได้เปลี่ยนจุด —3dB ของคอนเวอร์เตอร์ ซึ่งโดยทั่วไปคือ 675kHz อย่างเห็นได้ชัด ดังนั้น R1 และ C2 จึงไม่ถือเป็นตัวกรอง anti-aliasing หากคุณต้องการตัวกรอง anti-aliasing ในการประเมินของคุณ โดยทั่วไปควรวางไว้ก่อน LT1468 หรือตัวกรองภายนอกใดๆ ampตัวกระจายสัญญาณในเส้นทางสัญญาณ หากคุณมีส่วนประกอบความถี่ที่สูงกว่า Nyquist (1/2 fs) และสูงถึง 675KHz ส่วนประกอบเหล่านั้นจะพับกลับเข้าสู่ย่านความถี่ฐาน DC-125KHz และแยกไม่ออกจากสัญญาณในย่านความถี่นี้

หากคุณไม่มีเครื่องกำเนิดสัญญาณที่มีความแม่นยำระดับ ppm ของความถี่ คุณสามารถใช้ FFT พร้อมหน้าต่างเพื่อลด "การรั่วไหล" หรือการแพร่กระจายของปัจจัยพื้นฐาน เพื่อให้ได้ค่าประมาณที่ใกล้เคียงของพารามิเตอร์ประสิทธิภาพ ถ้าเป็น ampมีการใช้ lifier หรือแหล่งสัญญาณนาฬิกาที่มีสัญญาณรบกวนเฟสต่ำ หน้าต่างจะไม่ปรับปรุง SNR แหล่งสัญญาณที่โดยทั่วไปใช้สำหรับการทดสอบภายในคือ B&K 1051 แหล่งสัญญาณนาฬิกาภายในเพียงพอสำหรับการใช้งานส่วนใหญ่ เช่นเดียวกับ ADC ประสิทธิภาพสูง ส่วนนี้จะไวต่อโครงร่าง พื้นที่ที่อยู่รอบๆ ADC ทันทีควรใช้เป็นแนวทางในการจัดวาง และการกำหนดเส้นทางของส่วนประกอบต่างๆ ที่เกี่ยวข้องกับ ADC ควรคำนึงถึงระนาบพื้นที่ใช้ในโครงร่างของบอร์ดนี้ด้วย

วงจรสาธิต 1255

เอกสาร / แหล่งข้อมูล

|

วงจรสาธิตเทคโนโลยีเชิงเส้น 1255 16-BIT 25OKSPS ADC [พีดีเอฟ] คู่มือการใช้งาน 1255 16-BIT 25OKSPS ADC, วงจรสาธิต |